ASIC designers face the problem of integrating high performance IC parts onto a printed circuit board (PCB). The output driver circuit is most critical to the overall system performance. The demonstration file $installdir/demo/hspice/apps/asic1.sp shows the models for an output driver, the bond wire and leadframe, and a six inch length of copper transmission line.

This simulation demonstrates how to:

The Star-Hspice strategy is to:

* FILE: ASIC1.SP

* SIMULATE AN OUTPUT DRIVER DRIVING 6 INCHES OF 6MIL PRINTED

* CIRCUIT BOARD COPPER WITH 25PF OF LOAD CAPACITANCE

* MEASURE PEAK TO PEAK GROUND VOLTAGE

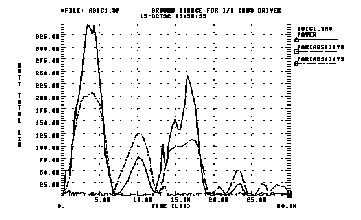

* MEASURE MAXIMUM GROUND CURRENT

* MEASURE MAXIMUM SUPPLY CURRENT

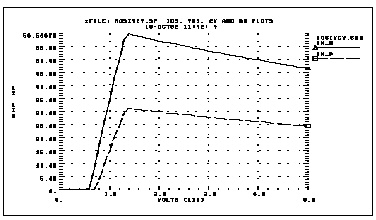

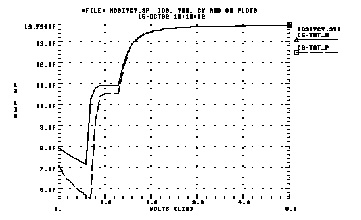

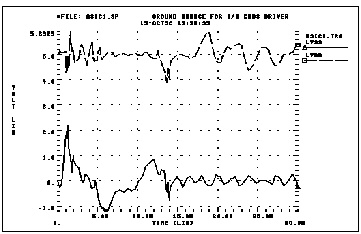

GROUND BOUNCE FOR I/O CMOS DRIVER 1200/1.2 & 800/1.2 MICRONS

.OPTIONS POST=2 RELVAR=.05

.TRAN .25N 30N

.MEASURE IVDD_MAX MAX PAR('ABS(I(VD))')

.MEASURE IVSS_MAX MAX PAR('ABS(I(VS))')

.MEASURE PEAK_GNDV PP V(LVSS)

.MEASURE PEAK_IVD PP PAR(' ABS(I(VD)*V(VDD,OUT)) ')

.MEASURE PEAK_IVS PP PAR(' ABS(I(VS)*V(VSS,OUT)) ')

.MEASURE RMS_POWER RMS POWER

.MEASURE FALL_TIME TRIG V(IN) RISE=1 VAL=2.5V

+ TARG V(OUT) FALL=1 VAL=2.5V

.MEASURE RISE_TIME TRIG V(IN) FALL=1 VAL=2.5V

+ TARG V(OUT) RISE=1 VAL=2.5V

.MEASURE TLINE_DLY TRIG V(OUT) RISE=1 VAL=2.5V

+ TARG V(OUT2) RISE=1 VAL=2.5V

VIN IN LGND PWL(0N 0V, 2N 5V, 12N 5, 14N 0)

* OUTPUT DRIVER

MP1 LOUT IN LVDD LVDD P W=1400U L=1.2U

MN1 LOUT IN LVSS LVSS N W=800U L=1.2U

xout LOUT OUT LEADFRAME

*POWER AND GROUND LINE PARASITICS

Vd VDD GND 5V

xdd vdd lvdd leadframe

Vs VSS gnd 0v

xss vss lvss leadframe

*OUTPUT LOADING -- 3 INCH FR-4 PC BOARD + 5PF LOAD +

*3 INCH FR-4 + 5PF LOAD

XLOAD1 OUT OUT1 GND LUMP5 LEN=3 WID=.006

CLOAD1 OUT1 GND 5PF

XLOAD2 OUT1 OUT2 GND LUMP5 LEN=3 WID=.006

CLOAD2 OUT2 GND 5PF

.macro leadframe in out

rframe in mid .01

lframe mid out 10n

cframe mid gnd .5p

.ends

*Tranmission Line Parameter Definitions

.param rho=.6mho/sq cap=.55nf/in**2 ind=60ph/sq

*The 5-lump macro defines a parameterized transmission line

.macro lump5 in out ref len_lump5=1 wid_lump5=.1

.prot

.param reseff='len_lump5*rho/wid_lump5*5'

+ capeff='len_lump5*wid_lump5*cap/5'

+ indeff='len_lump5*ind/wid_lump5*5'

r1 in 1 reseff

c1 1 ref capeff

l1 1 2 indeff

r2 2 3 reseff

c2 3 ref capeff

l2 3 4 indeff

r3 4 5 reseff

c3 5 ref capeff

l3 5 6 indeff

r4 6 7 reseff

c4 7 ref capeff

l4 7 8 indeff

r5 8 9 reseff

c5 9 ref capeff

l5 9 out indeff

.unprot

.ends

.MODEL N NMOS LEVEL=3 VTO=0.7 UO=500 KAPPA=.25 ETA=.03

+ THETA=.04 VMAX=2E5 NSUB=9E16 TOX=200E-10 GAMMA=1.5 PB=0.6 + + JS=.1M XJ=0.5U LD=0.0 NFS=1E11 NSS=2E10 capop=4

.MODEL P PMOS LEVEL=3 VTO=-0.8 UO=150 KAPPA=.25 ETA=.03

+ THETA=.04 VMAX=5E4 NSUB=1.8E16 TOX=200E-10 GAMMA=.672

+ PB=0.6 JS=.1M XJ=0.5U LD=0.0 NFS=1E11 NSS=2E10 capop=4

.end

IVDD_MAX = 0.1141 AT= 1.7226E-08

FROM= 0.0000E+00 TO= 3.0000E-08

IVSS_MAX = 0.2086 AT= 3.7743E-09

FROM= 0.0000E+00 TO= 3.0000E-08

PEAK_GNDV = 3.221 FROM= 0.0000E+00 TO= 3.0000E-08

PEAK_IVD = 0.2929 FROM= 0.0000E+00 TO= 3.0000E-08

PEAK_IVS = 0.3968 FROM= 0.0000E+00 TO= 3.0000E-08

RMS_POWER = 0.1233 FROM= 0.0000E+00 TO= 3.0000E-08

FALL_TIME = 1.2366E-09 TARG= 1.9478E-09 TRIG= 7.1121E-10

RISE_TIME = 9.4211E-10 TARG= 1.4116E-08 TRIG= 1.3173E-08

TLINE_DLY = 1.6718E-09 TARG= 1.5787E-08 TRIG= 1.4116E-08Star-Hspice Manual - Release 2001.2 - June 2001