The input netlist for the linear CMOS amplifier is shown below. The individual sections of the netlist are indicated using comment lines. Please refer to Specifying Simulation Input and Controls for information about the individual commands.

* Example HSPICE netlist using a linear CMOS amplifier

* netlist options

.option post probe brief nomod

* defined parameters

.param analog_voltage=1.0

* global definitions

.global vdd

* source statements

Vinput in gnd SIN ( 0.0v analog_voltage 10x )

Vsupply vdd gnd DC=5.0v

* circuit statements

Rinterm in gnd 51

Cincap in infilt 0.001

Rdamp infilt clamp 100

Dlow gnd clamp diode_mod

Dhigh clamp vdd diode_mod

Xinv1 clamp inv1out inverter

Rpull clamp inv1out 1x

Xinv2 inv1out inv2out inverter

Routterm inv2out gnd 100x

* subcircuit definitions

.subckt inverter in out

Mpmos out in vdd vdd pmos_mod l=1u w=6u

Mnmos out in gnd gnd nmos_mod l=1u w=2u

.ends

* model definitions

.model pmos_mod pmos level=3

.model nmos_mod nmos level=3

.model diode_mod d

* analysis specifications

.TRAN 10n 1u sweep analog_voltage lin 5 1.0 5.0

* output specifications

.probe TRAN v(in) v(clamp) v(inv1out) v(inv2out) i(dlow)

.measure TRAN falltime TRIG v(inv2out) VAL=4.5v FALL=1

+ TARG V(inv2out) VAL=0.5v FALL=1

.end

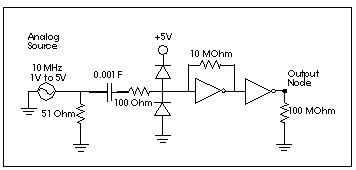

The following is the circuit diagram for the linear CMOS amplifier that is described in the circuit portion of the netlist. The two sources shown in the diagram are also in the netlist. Please note that the inverter symbols shown in the circuit diagram are constructed from two complementary MOSFET elements. Also, the diode and MOSFET models in the netlist were not given any non-default parameter values, except to specify Level 3 MOSFET models (empirical model).

The following section displays the various output files from a Star-Hspice simulation of the amplifier shown in the previous section. The simulation was executed by entering:

hspice example.sp > example.lis

where the input netlist was named example.sp and the output listing was named example.lis . The following output files were created with a brief explanation of their content.

The following subsections show the text files in their entirety for the amplifier simulation performed using Star-Hspice 1998.4 on a Sun workstation. The two post-processor output files cannot be shown because they are in binary format.

* "simulator" "HSPICE"

* "version" "98.4 (981215) "

* "format" "HSP"

* "rundate" "13:58:43 01/08/1999"

* "netlist" "example.sp "

* "runtitle" "* example hspice netlist using a linear cmos amplifier "

* time = 0.

* temperature = 25.0000

*** BEGIN: Saved Operating Point ***

.option

+ gmindc= 1.0000p

.nodeset

+ clamp = 2.6200

+ in = 0.

+ infilt = 2.6200

+ inv1out = 2.6200

+ inv2out = 2.6199

+ vdd = 5.0000

*** END: Saved Operating Point ***

Using: /net/sleepy/l0/group/hspice/98.4beta/sol4/hspice

****** Star-HSPICE -- 98.4 (981215) 13:58:43 01/08/1999 solaris

Copyright (C) 1985-1997 by Avant! Corporation.

Unpublished-rights reserved under US copyright laws.

This program is protected by law and is subject to the

terms and conditions of the license agreement found in:

/afs/rtp.avanticorp.com/product/hspice/current/license.txt

Use of this program is your acceptance to be bound by this

license agreement. Star-HSPICE is the trademark of

lic: FLEXlm:v5.12 USER:hspiceuser HOSTNAME:hspiceserv HOSTID:8086420f PID:1459

lic: Using FLEXlm license file:

lic: /afs/rtp/product/distrib/bin/license/license.dat

lic: Checkout hspice; Encryption code: AC34CE559E01F6E05809

lic: License/Maintenance for hspice will expire on 14-apr-1999/1999.200

lic: 1(in_use)/10 FLOATING license(s) on SERVER hspiceserv

* example hspice netlist using a linear cmos amplifier

.option post probe brief nomod

****** Star-HSPICE -- 98.4 (981215) 13:58:43 01/08/1999 solaris ******

* example hspice netlist using a linear cmos amplifier

****** transient analysis tnom= 25.000 temp= 25.000 ******

*** parameter analog_voltage = 1.000E+00 ***

node =voltage node =voltage node =voltage

+0:clamp = 2.6200 0:in = 0. 0:infilt = 2.6200

+0:inv1out = 2.6200 0:inv2out = 2.6199 0:vdd = 5.0000

**warning** negative-mos conductance = 1:mnmos iter= 2

gm,gds,gmbs,ids= -3.636E-05 1.744E-04 0. 1.598E-04

* example hspice netlist using a linear cmos amplifier

****** transient analysis tnom= 25.000 temp= 25.000 ******

falltime= 3.9149E-08 targ= 7.1916E-08 trig= 3.2767E-08

****** Star-HSPICE -- 98.4 (981215) 13:58:43 01/08/1999 solaris ******

* example hspice netlist using a linear cmos amplifier

****** transient analysis tnom= 25.000 temp= 25.000 ******

*** parameter analog_voltage = 2.000E+00 ***

node =voltage node =voltage node =voltage

+0:clamp = 2.6200 0:in = 0. 0:infilt = 2.6200

+0:inv1out = 2.6200 0:inv2out = 2.6199 0:vdd = 5.0000

* example hspice netlist using a linear cmos amplifier

****** transient analysis tnom= 25.000 temp= 25.000 ******

falltime= 1.5645E-08 targ= 5.7994E-08 trig= 4.2348E-08

****** Star-HSPICE -- 98.4 (981215) 13:58:43 01/08/1999 solaris ******

* example hspice netlist using a linear cmos amplifier

****** transient analysis tnom= 25.000 temp= 25.000 ******

*** parameter analog_voltage = 3.000E+00 ***

node =voltage node =voltage node =voltage

+0:clamp = 2.6200 0:in = 0. 0:infilt = 2.6200

+0:inv1out = 2.6200 0:inv2out = 2.6199 0:vdd = 5.0000

* example hspice netlist using a linear cmos amplifier

****** transient analysis tnom= 25.000 temp= 25.000 ******

falltime= 1.1917E-08 targ= 5.6075E-08 trig= 4.4158E-08

****** Star-HSPICE -- 98.4 (981215) 13:58:43 01/08/1999 solaris ******

* example hspice netlist using a linear cmos amplifier

****** transient analysis tnom= 25.000 temp= 25.000 ******

*** parameter analog_voltage = 4.000E+00 ***

node =voltage node =voltage node =voltage

+0:clamp = 2.6200 0:in = 0. 0:infilt = 2.6200

+0:inv1out = 2.6200 0:inv2out = 2.6199 0:vdd = 5.0000

* example hspice netlist using a linear cmos amplifier

****** transient analysis tnom= 25.000 temp= 25.000 ******

falltime= 7.5424E-09 targ= 5.3989E-08 trig= 4.6447E-08

****** Star-HSPICE -- 98.4 (981215) 13:58:43 01/08/1999 solaris ******

* example hspice netlist using a linear cmos amplifier

****** transient analysis tnom= 25.000 temp= 25.000 ******

*** parameter analog_voltage = 5.000E+00 ***

node =voltage node =voltage node =voltage

+0:clamp = 2.6200 0:in = 0. 0:infilt = 2.6200

+0:inv1out = 2.6200 0:inv2out = 2.6199 0:vdd = 5.0000

* example hspice netlist using a linear cmos amplifier

****** transient analysis tnom= 25.000 temp= 25.000 ******

falltime= 6.1706E-09 targ= 5.3242E-08 trig= 4.7072E-08

mean = 16.0848n varian = 1.802e-16

sigma = 13.4237n avgdev = 9.2256n

****** Star-HSPICE -- 98.4 (981215) 13:58:43 01/08/1999 solaris ******

* example hspice netlist using a linear cmos amplifier

****** job statistics summary tnom= 25.000 temp= 25.000 ******

# diodes= 2 # bjts = 0 # jfets = 0 # mosfets = 4

analysis time # points tot. iter conv.iter

transient 4.71 505 9322 2624 rev= 664

job started at 13:58:43 01/08/1999

job ended at 13:58:50 01/08/1999

HSPICE job example.sp completed.

***** Star-HSPICE -- 98.4 (981215) 13:58:43 01/08/1999 solaris

lic: FLEXlm:v5.12 USER:hspiceuser HOSTNAME:hspiceserv HOSTID:8086420f PID:1459

lic: Using FLEXlm license file:

lic: /afs/rtp/product/distrib/bin/license/license.dat

lic: Checkout hspice; Encryption code: AC34CE559E01F6E05809

lic: License/Maintenance for hspice will expire on 14-apr-1999/1999.200

lic: 1(in_use)/10 FLOATING license(s) on SERVER hspiceserv

init: begin read circuit files, cpu clock= 2.21E+00

init: end read circuit files, cpu clock= 2.23E+00 memory= 145 kb

init: begin check errors, cpu clock= 2.23E+00

init: end check errors, cpu clock= 2.24E+00 memory= 144 kb

init: begin setup matrix, pivot= 10 cpu clock= 2.24E+00

establish matrix -- done, cpu clock= 2.24E+00 memory= 146 kb

re-order matrix -- done, cpu clock= 2.24E+00 memory= 146 kb

init: end setup matrix, cpu clock= 2.25E+00 memory= 154 kb

sweep: parameter parameter1 begin, #sweeps= 5

parameter: analog_voltage = 1.00E+00

dcop: begin dcop, cpu clock= 2.25E+00

dcop: end dcop, cpu clock= 2.27E+00 memory= 154 kb tot_iter= 11

sweep: tran tran1 begin, stop_t= 1.00E-06 #sweeps= 101 cpu clock= 2.28E+00

tran: time= 1.03750E-07 tot_iter= 78 conv_iter= 24

tran: time= 2.03750E-07 tot_iter= 179 conv_iter= 53

tran: time= 3.03750E-07 tot_iter= 280 conv_iter= 82

tran: time= 4.03750E-07 tot_iter= 381 conv_iter= 111

tran: time= 5.03750E-07 tot_iter= 482 conv_iter= 140

tran: time= 6.03750E-07 tot_iter= 583 conv_iter= 169

tran: time= 7.03750E-07 tot_iter= 684 conv_iter= 198

tran: time= 8.03750E-07 tot_iter= 785 conv_iter= 227

tran: time= 9.03750E-07 tot_iter= 886 conv_iter= 256

tran: time= 1.00000E-06 tot_iter= 987 conv_iter= 285

sweep: tran tran1 end, cpu clock= 2.82E+00 memory= 155 kb

parameter: analog_voltage = 2.00E+00

dcop: begin dcop, cpu clock= 2.83E+00

dcop: end dcop, cpu clock= 2.83E+00 memory= 155 kb tot_iter= 14

sweep: tran tran2 begin, stop_t= 1.00E-06 #sweeps= 101 cpu clock= 2.83E+00

tran: time= 1.01016E-07 tot_iter= 186 conv_iter= 54

tran: time= 2.02642E-07 tot_iter= 338 conv_iter= 98

tran: time= 3.01763E-07 tot_iter= 495 conv_iter= 145

tran: time= 4.04254E-07 tot_iter= 668 conv_iter= 198

tran: time= 5.02594E-07 tot_iter= 841 conv_iter= 248

tran: time= 6.10102E-07 tot_iter= 983 conv_iter= 289

tran: time= 7.01850E-07 tot_iter= 1161 conv_iter= 340

tran: time= 8.01776E-07 tot_iter= 1306 conv_iter= 383

tran: time= 9.04268E-07 tot_iter= 1481 conv_iter= 436

tran: time= 1.00000E-06 tot_iter= 1654 conv_iter= 486

sweep: tran tran2 end, cpu clock= 3.71E+00 memory= 155 kb

parameter: analog_voltage = 3.00E+00

dcop: begin dcop, cpu clock= 3.71E+00

dcop: end dcop, cpu clock= 3.72E+00 memory= 155 kb tot_iter= 17

sweep: tran tran3 begin, stop_t= 1.00E-06 #sweeps= 101 cpu clock= 3.72E+00

tran: time= 1.00313E-07 tot_iter= 143 conv_iter= 42

tran: time= 2.01211E-07 tot_iter= 340 conv_iter= 100

tran: time= 3.01801E-07 tot_iter= 539 conv_iter= 156

tran: time= 4.02192E-07 tot_iter= 729 conv_iter= 211

tran: time= 5.01997E-07 tot_iter= 917 conv_iter= 265

tran: time= 6.01801E-07 tot_iter= 1088 conv_iter= 314

tran: time= 7.01801E-07 tot_iter= 1221 conv_iter= 351

tran: time= 8.01801E-07 tot_iter= 1362 conv_iter= 392

tran: time= 9.02387E-07 tot_iter= 1515 conv_iter= 435

tran: time= 1.00000E-06 tot_iter= 1674 conv_iter= 479

sweep: tran tran3 end, cpu clock= 4.57E+00 memory= 155 kb

parameter: analog_voltage = 4.00E+00

dcop: begin dcop, cpu clock= 4.57E+00

sweep: tran tran4 begin, stop_t= 1.00E-06 #sweeps= 101 cpu clock= 4.58E+00

tran: time= 1.00110E-07 tot_iter= 236 conv_iter= 70

tran: time= 2.04376E-07 tot_iter= 475 conv_iter= 139

tran: time= 3.07892E-07 tot_iter= 767 conv_iter= 221

tran: time= 4.01056E-07 tot_iter= 951 conv_iter= 273

tran: time= 5.01086E-07 tot_iter= 1250 conv_iter= 353

tran: time= 6.00965E-07 tot_iter= 1541 conv_iter= 432

tran: time= 7.03668E-07 tot_iter= 1805 conv_iter= 506

tran: time= 8.01114E-07 tot_iter= 2046 conv_iter= 571

tran: time= 9.01005E-07 tot_iter= 2308 conv_iter= 640

tran: time= 1.00000E-06 tot_iter= 2528 conv_iter= 703

sweep: tran tran4 end, cpu clock= 5.83E+00 memory= 155 kb

parameter: analog_voltage = 5.00E+00

dcop: begin dcop, cpu clock= 5.83E+00

dcop: end dcop, cpu clock= 5.84E+00 memory= 155 kb tot_iter= 23

sweep: tran tran5 begin, stop_t= 1.00E-06 #sweeps= 101 cpu clock= 5.84E+00

tran: time= 1.00195E-07 tot_iter= 176 conv_iter= 47

tran: time= 2.00617E-07 tot_iter= 431 conv_iter= 115

tran: time= 3.00475E-07 tot_iter= 661 conv_iter= 176

tran: time= 4.00719E-07 tot_iter= 914 conv_iter= 246

tran: time= 5.04084E-07 tot_iter= 1157 conv_iter= 311

tran: time= 6.00666E-07 tot_iter= 1347 conv_iter= 363

tran: time= 7.01830E-07 tot_iter= 1623 conv_iter= 435

tran: time= 8.02418E-07 tot_iter= 1900 conv_iter= 514

tran: time= 9.01178E-07 tot_iter= 2161 conv_iter= 585

tran: time= 1.00000E-06 tot_iter= 2410 conv_iter= 650

sweep: tran tran5 end, cpu clock= 7.03E+00 memory= 155 kb

sweep: parameter parameter 1 end

>info: ***** hspice job concluded

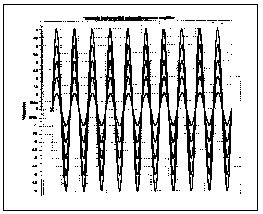

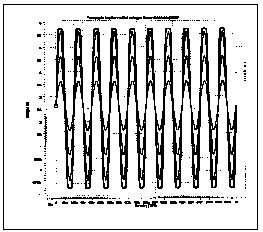

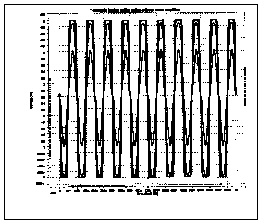

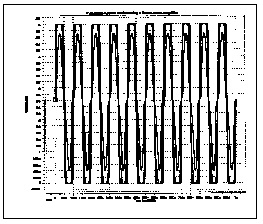

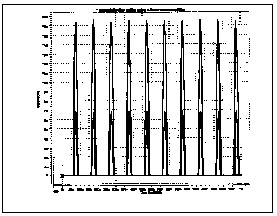

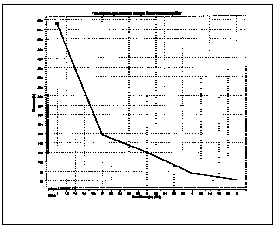

The following plots show the six different post-processor outputs from the simulation of the example netlist, as seen in AvanWaves, the graphical waveform viewer available from Avant! These plots are postscript output from the actual data.