# **Power Dissipation**

Power Dissipation Active Versus Passive Power "On" and "Off" Currents High–K Dielectrics Low-K Dielectrics

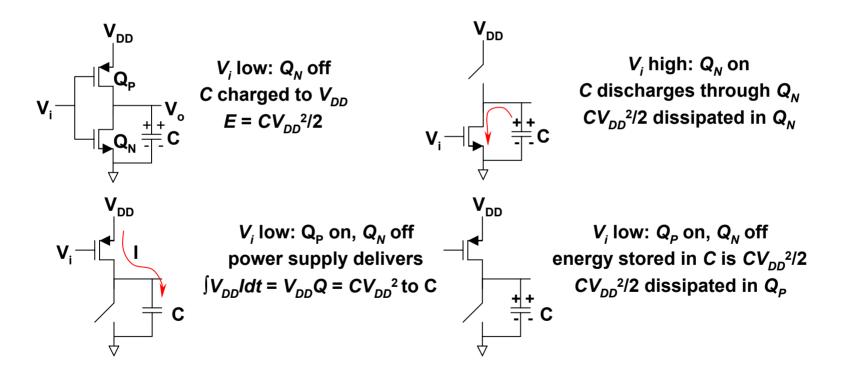

## **CMOS Power Dissipation**

- CMOS is popular because it is a low power technology

- The main power dissipation occurs during switching

$CV_{DD}^{2}$  total power dissipated

## **CMOS** Power Dissipation

Power dissipation sources:

$$\boldsymbol{P} = \boldsymbol{P}_{switch} + \boldsymbol{P}_{sc} + \boldsymbol{P}_{off}$$

$$P_{switch} = \alpha f C V_{DD}^2; P_{sc} = I_{sc} V_{DD}; P_{off} = I_{off} V_{DD}$$

$\alpha$ : switching activity;  $I_{sc}$ : short circuit path when n and p-channel MOSFETs are "on"  $I_{off}$ : drain leakage current and subthreshold leakage current when device is "off"

#### Reduce power by reducing

- Supply voltage  $V_{DD}$   $\Downarrow$ ; need to reduce  $V_{T}$  to maintain drive current

- Capacitance C

- Off current I<sub>off</sub> depends on V<sub>T</sub>

- Frequency  $f \Downarrow$ ; parallel architectures

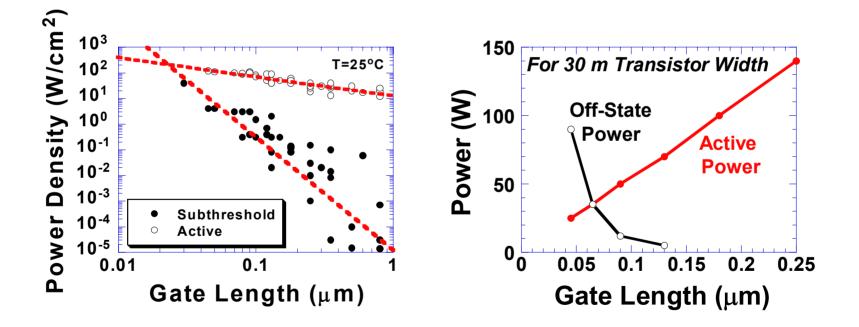

#### **Active Versus Passive Power**

• As  $V_T$  decreases,  $I_{off}$  increases  $\Rightarrow P_{off}$  increases

E.J. Nowak, IBM J. Res. Dev. 46, 169 (2002)

B. Doyle, Intel Technol. J. 41 (May 2002)

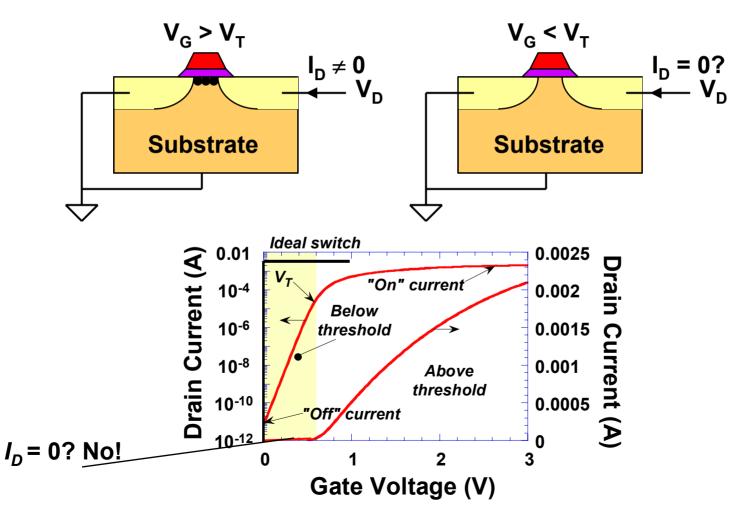

### **MOSFET Switch**

In a digital circuit, a MOSFET is frequently used as a switch

### "On" – "Off" Current

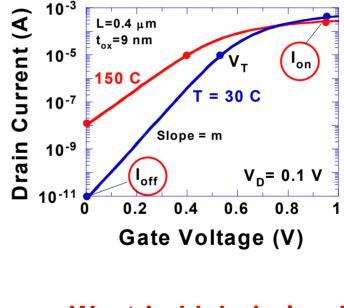

#### Subhreshold

Subthreshold slope = m; Subthreshold swing S = 1/m

$$I_D = I_T \mathbf{e}^{q(V_G - V_T)/nkT}$$

$$I_{off}(V_G = \mathbf{0}) = I_T \mathbf{e}^{-qV_T/nkT}$$

$$S = \frac{dV_G}{d[\log(I_D)]} = \frac{2.3nkT}{q}$$

$$= 60n(T/300) mV/decade of I_D$$

Above threshold

$$\boldsymbol{I}_{Dsat} = \boldsymbol{I}_{on} = \frac{\boldsymbol{W}\mu_{eff}\boldsymbol{C}_{ox}}{2\boldsymbol{L}}(\boldsymbol{V}_{G} - \boldsymbol{V}_{T})^{2}$$

Want I<sub>on</sub> high, I<sub>off</sub> low !

## "On" Current

- W/L ~ constant

- $\mu_{eff} \sqrt[]{}$

Reduced drive current

- V<sub>G</sub> ↓

- Reduced electric field

- Reduced power

- Reduced drive current

- Increased delay time

- V<sub>7</sub> ∿

- Increased drive current

- Increased "off" current

$$\boldsymbol{I}_{on} = \frac{\boldsymbol{W}}{2\boldsymbol{L}} \boldsymbol{\mu}_{eff} \boldsymbol{C}_{ox} (\boldsymbol{V}_{G} - \boldsymbol{V}_{T})^{2}$$

- C<sub>ox</sub> û since t<sub>ox</sub> ↓

- Increased drive current

- Oxide leakage current

- Boron penetration

#### Ion should not decrease!

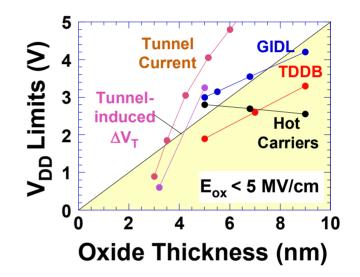

## **Power Supply Voltage Limit**

- *E<sub>ox</sub>* ≈ 4 5 MV/cm

- Power supply voltage is limited by

- Power dissipation

- Oxide leakage current

- Gate-induced drain leakage current (GIDL)

- Time-dependent dielectric breakdown

- Hot carrier effects

- Delay time

Data after: T. Hori, *Gate Dielectrics and MOS ULSIs*, Springer, 1997.

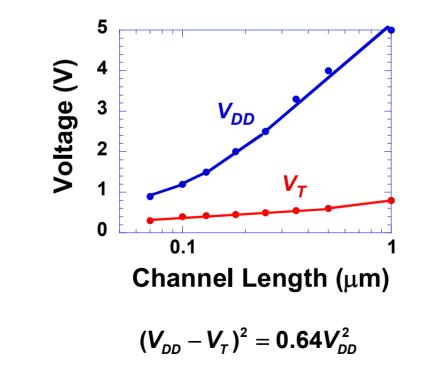

## **Threshold and Supply Voltages**

- How has V<sub>T</sub> changed with V<sub>DD</sub>? Less than called for by scaling rules

- V<sub>DD</sub> V<sub>T</sub> is continually decreasing

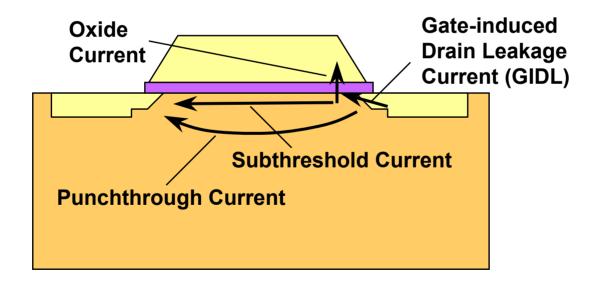

## **"Off" Current**

The "off" current is due to subthreshold, punchtrough, gate-induced drain leakage, and oxide currents

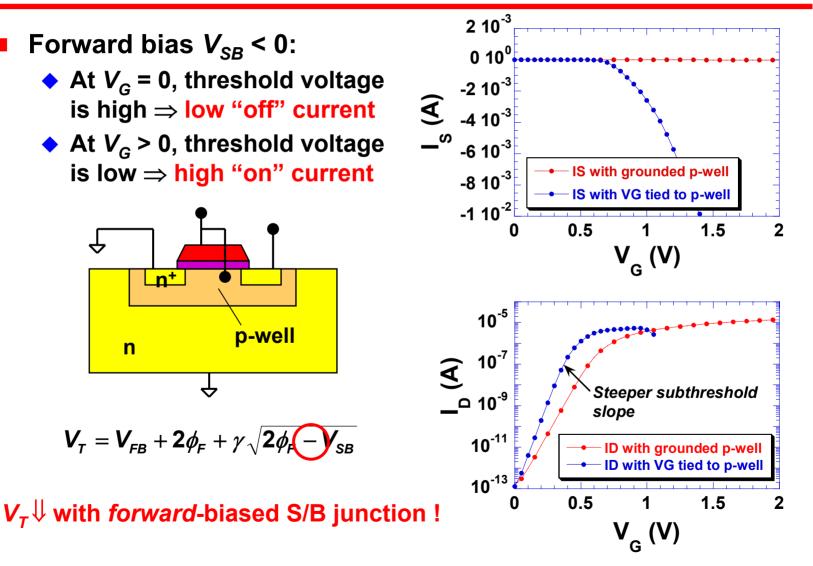

#### **Positive Substrate Bias**

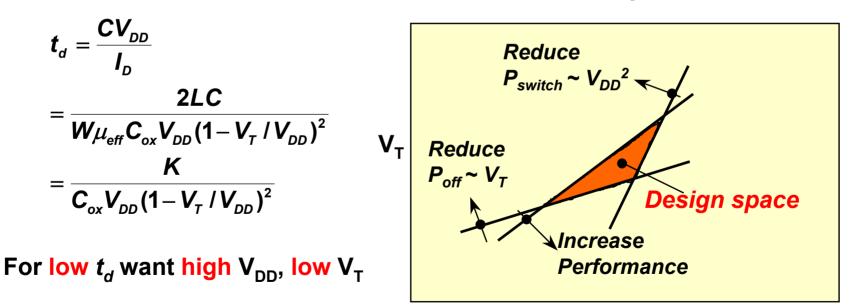

## **Propagation Delay Time**

- Conflicting design requirements between reducing V<sub>DD</sub>, V<sub>T</sub>, I<sub>leak</sub>, C, and increasing performance

- The propagation delay time is  $t_d = \frac{C \Delta V}{I}$

V<sub>DD</sub>

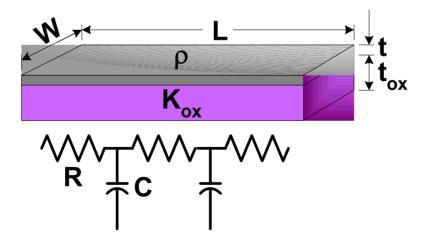

### **Low - K Dielectrics**

- Propagation delay along interconnects requires reduced K<sub>ox</sub>

- Ideally K = 1 (air)

- Practically K < 3.5</p>

$$\tau = \mathbf{R}\mathbf{C} = \frac{\rho \mathbf{L}}{\mathbf{W}t} \frac{\mathbf{K}_{ox} \varepsilon_{o} \mathbf{L} \mathbf{W}}{\mathbf{t}_{ox}} = \frac{\rho \mathbf{K}_{ox} \varepsilon_{o} \mathbf{L}^{2}}{\mathbf{t}_{ox}}$$

Need low  $\rho$  and low  $K_{ox}$

## **Low - K Dielectrics**

Low-K dielectrics reduce wiring capacitance ⇒ reduce power

$P = \alpha C f V^2$

- Low-K dielectrics tend to be "fluffy"

- To reduce the dielectric constant, introduce air pockets into the material

- Dielectric constant

- Hardness

- Adhesion

- Thermal expansion

- Process compatibility

- Swelling

## Low – K Materials

| K Value | Organic Polymers | Silsesquioxane<br>Based | Silica Based       |

|---------|------------------|-------------------------|--------------------|

| 4.2     |                  |                         | SiO <sub>2</sub>   |

| 3 – 4   |                  | FOX™                    | Fluorinated Silica |

| 2.4 – 3 | FLARE™           | HOSP™                   | Aurora™            |

|         | BCB              |                         | Coral™             |

|         | SiLK™            |                         | Z3MS™              |

|         |                  |                         | Black Diamond™     |

| 2 – 2.4 | Porous SiLK™     | IPS™                    | Orion™             |

|         | PTFE             | LKD™                    | Nanoglass™         |

|         |                  | XLK™                    |                    |

|         |                  | Zirkon™                 |                    |

| < 2     |                  |                         | Aerogel            |

|         |                  |                         | Xerogel            |

K. Maex et al., "Low Dielectric Constant Materials for Microelectronics," *J. Appl. Phys.* **93**, 8793-8841, June 2003.

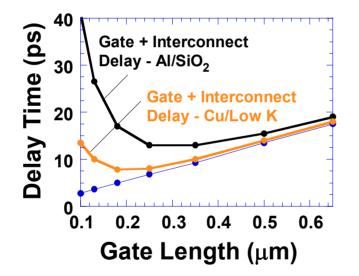

## **Propagation Delay**

Propagation delay depends on metal conductivity and interlevel dielectric constant

AI:  $\rho = 3 \mu\Omega$ -cm Cu:  $\rho = 1.7 \mu\Omega$ -cm SiO<sub>2</sub>:  $K_{ox} = 4$ Low K:  $K_{ox} = 2$ AI/Cu: 0.8 μm thick AI/Cu: 43 μm long

Why do we need high-K dielectrics?

$$I_{D} = \frac{W\mu_{eff}C_{ox}}{L}(V_{G} - V_{T})^{2} = \frac{W\mu_{eff}K_{ox}\mathcal{E}_{o}}{Lt_{ox}}(V_{G} - V_{T})^{2}$$

- With scaling

- W and L decrease same amount

- $\bullet$   $\mu_{eff}$  remains about the same or decreases

- ♦ (V<sub>G</sub>-V<sub>T</sub>) decreases

- To keep drain current constant

- *t<sub>ox</sub>* decreases oxide leakage current increases

- *K<sub>ox</sub>* increases thicker insulator, reduced oxide leakage current

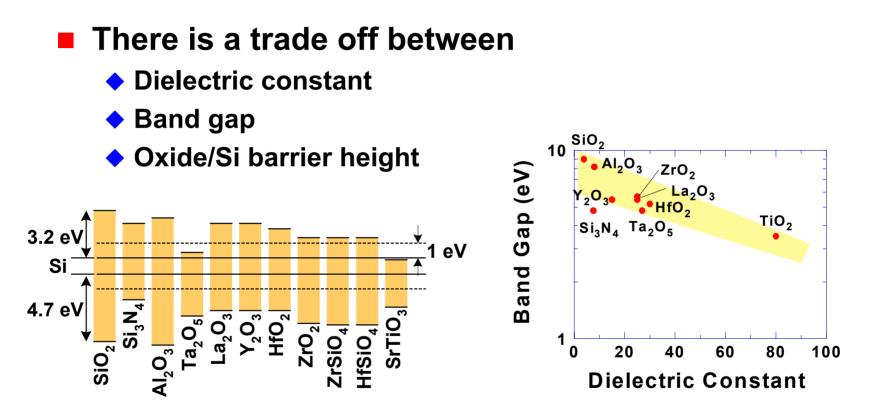

- The dielectric constant, band gap and dielectric/Si barrier height are important

- Tunneling probability

$$\boldsymbol{T} = \exp\left(-2t_{\rm ox}\sqrt{\frac{2q\boldsymbol{m}^{*}\boldsymbol{\phi}_{\rm B}}{\hbar^{2}}}\right)$$

#### Need

- High dielectric constant

- High band gap

- High barrier at insulator/Si interface

- Low leakage current

- High reliability

- Good insulator/Si interface quality

- Low flatband voltage shift

#### HfO<sub>2</sub> and nitrided HfO<sub>2</sub> most promising

J. Robertson, J. Vac. Sci. Technol. B18, 1785 (2000)

#### Problems

- Low band gap

- Low barrier height

- Poor insulator/Si interface

- Thin intervening SiO<sub>2</sub> layer

- Oxide charge

- Low electron/hole mobility

- Strained Si

- MOS process compatible ?

- What determines CMOS power dissipation?

- What are "on" and "off" currents

- What determines propagation delay time?

- Why do we need low-K dielectrics?

- Why do we need high-K dielectrics?

- What are the conflicting demands of high on current and low off current?

- What are the conflicting demands of CMOS power dissipation and propagation delay time?